Navi 4C o RDNA 4X, así iba a ser la cancelada RX 8000 Top

Una información reciente ha traído de nuevo a la cancelada GPU topé de gama de AMD para las RX 8000, la llamada Navi 4C o RDNA 4X, es por ello que hemos decidido hacer un repaso sobre este chip gráfico, dado que configuración podríamos verla en futuras tarjetas gráficas, así como potencialmente en la siguiente generación de consolas.

Índice de contenidos

¿Navi 4C o RDNA 4X iba a tener 9 Shader Engines?

Tradicionalmente, bajo el nombre de IOD se encuentra el chiplet donde se encuentra el controlador de memoria integrado, por lo que cuando hablamos la GPU, el MCD es prácticamente lo mismo, con la diferencia de que este alberga la caché, la L3 o Infinity Caché en el caso de las RX 7000 de gama alta, es decir, los basados en los chips Navi 31 y Navi 32.

Sin embargo, uno de los planes de AMD a futuro, el cual teníamos que ver en el cancelado Navi 4C o RDNA 4X era la adopción del mismo IOD que trae consigo el MI300, el cual tiene la particularidad no solo de encargarse de la interconexión entre los chiplets, sino también de hacer el trabajo de los MCD. Es decir, albergan también la caché de último nivel.

Ahora bien, en los foros de Anandtech ha aparecido información de esta GPU, en concreto na parte de los drivers de AMD, donde se puede deducir, una teoría, una configuración de 9 SED (Shader Engine Die), una conclusión que nos parece, cuando menos errónea. Claro está que afirmaciones extraordinarias requieren demostraciones del mismo calibre.

¿Por qué dicha afirmación es errónea?

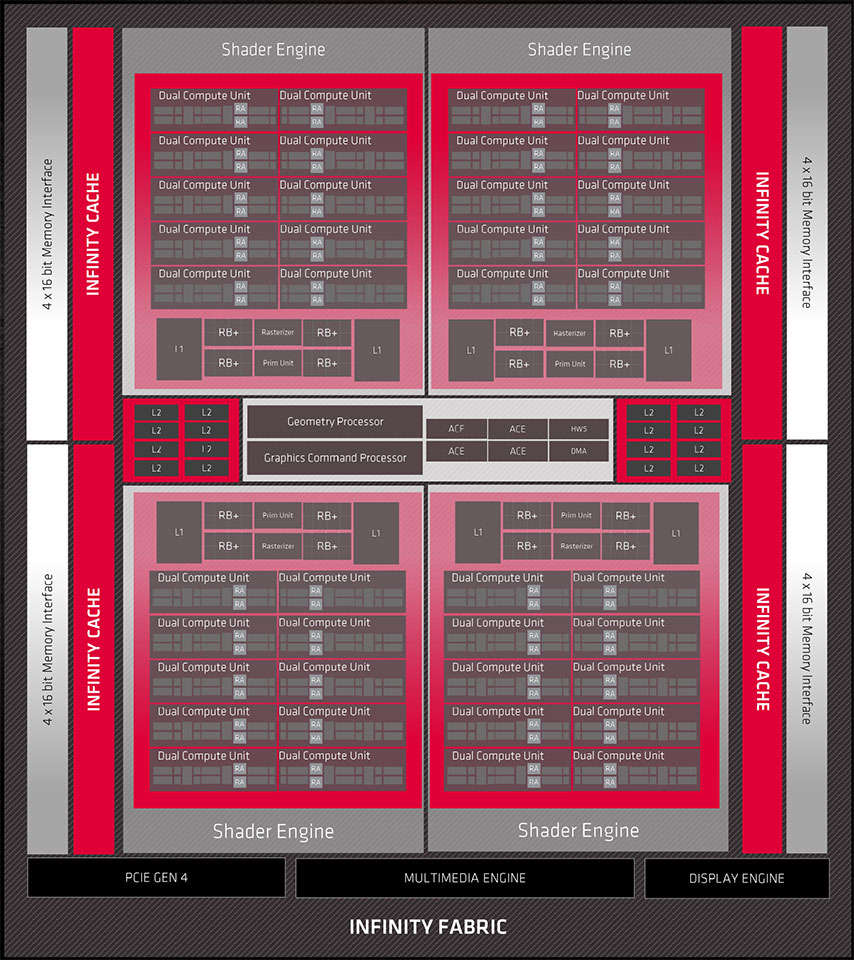

Empecemos por el hecho que el GCD, si hacemos caso a ciertas patentes y filtraciones que se dieron antes de la cancelación Navi 4C o RDNA 4X, entonces tenemos que este se divide en tres elementos distintos:

- SED: el cual dispone un Shader Engine, incluyendo sus cachés, hasta la de segundo nivel.

- AID/IOD: el interposer activo sobre el que van el resto de chiplets, se encarga de su intercomunicación, así como de albergar la caché L3 o Infinity Caché y de encargarse de la comunicación externa con la VRAM.

- MMIOD: Un chiplet que alberga los coprocesadores de apoyo de la GPU (unidades DMA, códecs de vídeo, controladores de pantalla.

- Bridge Chiplets: que comunicaban el primer AID/IOD con el segundo y este con el tercero, permitiendo escalar la configuración

Por si no lo veis, os lo vamos a poner más fácil para que veáis a que nos referimos.

Antes de nada, perdón por cómo se ve la imagen. A lo que nos referimos es que en la especulación sobre como iba a ser Navi 4C o RDNA 4X es que se olvidan de algo tan esencial como el procesador de comandos. Por lo que estaríamos hablamos de una configuración de 1+8, donde el procesador de comandos se encuentra en la parte central, y los otros 8 chiplets alrededor son los SED. Con ello, cada dos Shader Engine Die tienen asignado en el IOD un controlador de memoria GDDR6 de 64 bits, para una configuración de 512 bits.

¿Está la idea realmente cancelada?

Pues por las informaciones que tenemos, si bien no vamos a ver el chip Navi 4C o RDNA 4X para la siguiente generación, lo que está claro es que llegará para la siguiente generación con lo que será una versión actualizada. El motivo de ello es simple, y se ha visto con la RTX 4090 de NVIDIA y se verá con la RTX 5090 de la misma marca, tal nivel de especificaciones supera por mucho lo necesario actualmente incluso en los videojuegos más punteros.

En todo caso, lo más seguro es que con la adopción de la GDDR7, el bus de memoria pase de los 512 bits a los 256 bits, lo que reducirá el número de chips y de la complejidad en placa. Ya para terminar, si os preguntáis que sentido tiene subdividir en chiplets, la razón es por el alto precio de los nodos de fabricación que se vienen y la versatilidad que da ir variando el número de chiplets para diferentes configuraciones. En todo caso, para RDNA 5 todavía deberemos esperar un par de años para verlo y, lo más seguro es que será la base para PlayStation 6, hasta el momento, paciencia.