Zen 5, ¿se ha convertido AMD en la liebre esta vez?

Seguimos con las tecnologías presentadas en la Computex, esta vez le toca el turno al AMD Zen 5, cuya nueva información nos ha hecho reescribir buena parte del artículo que publicamos hace unos meses, las cuales se basaban principalmente en rumores. Se puede decir, y sin ganas de quitarle méritos a la empresa de Lisa Su, que de los tres nuevos núcleos x86 es el que más fríos nos ha dejado, pero más que nada por seguir una estela más conservadora. Lo cual no quita que los cambios respecto a Zen 4 no sean interesantes.

Índice de contenidos

AMD parte esta vez con desventaja frente a Intel

Y el motivo no es la arquitectura del AMD Zen 5, sino el hecho que Intel ha podido optar para sus nuevos núcleos litografías más avanzadas que su rival, la cual se ha quedado en el nodo de “4 nm” de TSMC, mientras que tenemos la Compute Tile de Lunar Lake el de “3 nm” y veremos a Arrow Lake bajo la tecnología Intel 20A, que corresponde a una litografía de “2 nm”. Esto supone una desventaja que ha hecho que AMD tenga menos margen de mejora respecto a Zen 4.

Desconocemos el motivo por el cual AMD ha decidido escoger dicha litografía, lo único que podemos decir es que buena parte de los diseños hechos en el nodo N5 de “5 nm” se pueden trasladar fácilmente a N4. Lo que supone un ahorro en tiempo y dinero, por lo que la deducción es que los de Lisa Su con tal de cumplir con el timing de 2 años clásico entre núcleo y núcleo han optado por dicha litografía.

Sin embargo, desde cierto punto de vista la elección de Lisa Su es entendible. Los nodos más avanzados tienen un coste por oblea mucho más caro, y los yields, lo cual mide la cantidad de chips buenos por oblea, es mucho más alto. En otras palabras, la idea detrás de AMD Zen 5 es ser más competitivos en precio.

El nuevo Frontend en AMD Zen 5

Una de las decisiones que se han tomado en AMD Zen 5 por parte de sus arquitectos es realizarle un lavado de cara a su Frontend, es decir, la parte de la CPU encargada de captar, decodificar y distribuir las diferentes instrucciones a las unidades de ejecución. Todo ello tiene sentido por el hecho que durante generaciones dicha parte se había quedado en una media cercana de 4 instrucciones, aunque en los últimos tiempos, especialmente con los saltos a Zen 3 primero y Zen 4 después, este se había movido a las 5 instrucciones y pico.

Sin embargo, 6 es un número feo al que Intel ya había llegado con anterioridad y se ha de tener en cuenta que la capacidad de manejar hasta 8 instrucciones simultáneas en el Frontend del Apple M1 es lo que ha motivado no solo a los ingenieros de Intel, sino también a los de su rival. ¿El mayor cambio en el AMD Zen 5? La parte dedicada a la decodificación de instrucciones se ha duplicado, pero esta vez para tener la capacidad de entregar esas 8 instrucciones al igual que sus rivales directos.

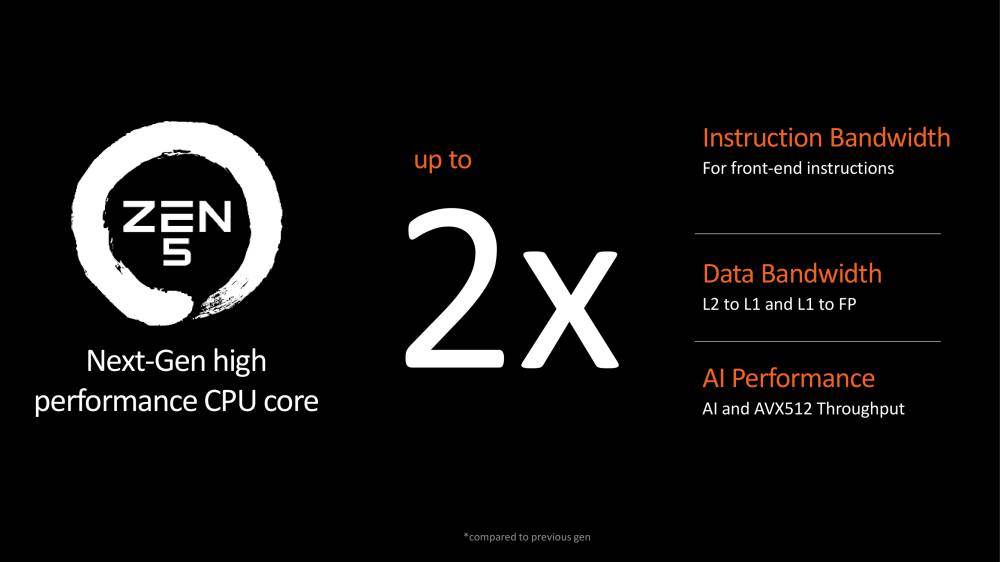

Mejoras en coma flotante y AVX-512, pero no en enteros

La adopción por parte de AMD de las instrucciones AVX-512 en Zen 4 es cuando menos polémica, en especial en el campo de la IA, donde el uso de GPU con capacidades para ello y de NPU después, hacen que el subconjunto VNNI, dedicado especialmente al Deep Learning, haya quedado desfasado. Por lo que, en la presentación de la Computex de 2024 de AMD, quien escribe esto, se quedó un poco con cara de póker cuando vio la siguiente diapositiva:

Os explico, las instrucciones SIMD realmente es la capacidad de ejecutar una misma instrucción en varios datos distintos. Por lo que si tenemos dos unidades SIMD de 256 bits podemos ejecutar una instrucción SIMD de 512 bits. Una estrategia no solo adoptada por AMD sino también por Intel. Pues bien, dado que hasta en el Hot Chips de este año no veremos todos los detalles de AMD Zen 5, nuestra conclusión es que en coma flotante y unidades SIMD han duplicado el número de unidades. De ahí el hecho de haber duplicado el ancho de banda desde la caché L2 de cada núcleo

Sin embargo, el jarro de agua fría, el cual sería el precio a pagar por usar una litografía menos avanzada, es que el pipeline de enteros se mantendría idéntico al de Zen 4. Al menos esto es lo que podemos deducir por el momento.

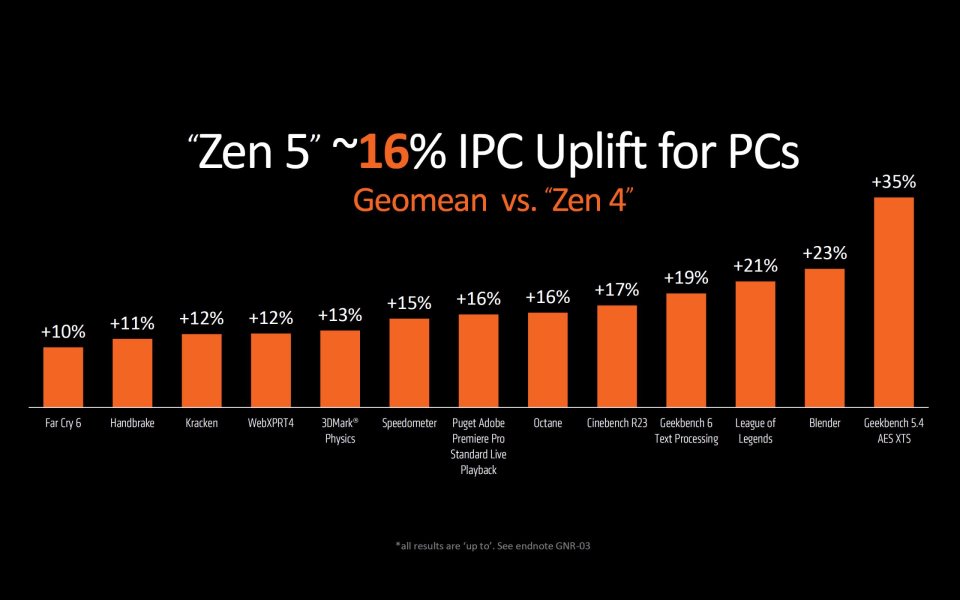

La polémica del IPC en AMD Zen 5

Uno de los mayores problemas de la mente humana es que es incapaz de saber si algo es peor o mejor sin un valor cardinal de su rendimiento que le sirva para compararlo con otras soluciones al mismo problema. No obstante, el diferencial en el IPC no es constante entre las diferentes pruebas de rendimiento, y, por lo general, en la industria se suele usar SPECINT 2017 y SPECFP 2017 para la comparación entre núcleos, lo que no quita que existan otras pruebas de rendimiento.

Pues bien, en los últimos meses los zelotes de AMD en las redes decidieron llenar la red diciendo que el IPC en AMD Zen 5 iba a ser mayor del 30%. Incluso después de la presentación de hace unos días siguieron teniendo la desfachatez de hacerlo. Un salto que, de ser verdad, sería espectacular y comparable como el que vimos en el primer núcleo Zen.

No obstante, la realidad es muy diferente a eso y dicha cifra corresponde a un benchmark concreto y la cifra oficial es un salto del 16% respecto a Zen 4, pero no especifican si en coma flotante o en enteros. Si partimos del hecho de que Lion Cove es un 14% más potente que Redwood Cove, y que Zen 4 se encuentra por encima, entonces está claro que en cuanto a núcleos de rendimiento Zen 5 es el más potente hasta la fecha, ¿o no?