El CTO de AMD da una pista vedada sobre las consolas de próxima generación

Hasta ahora los chips disgregados, los que se componen de varias piezas o chiplets en vez de una, vienen de un mismo proveedor, aunque hablemos de que cada parte se fabrique en una fundición distinta. Sin embargo, en el futuro esto cambiará y todo ello gracias al estándar UCIe, el cual marcará como se creará este tipo de hardware en un futuro.

Índice de contenidos

Tabla de contenidos

¿Qué es UCIe y que relación tiene con los chiplets?

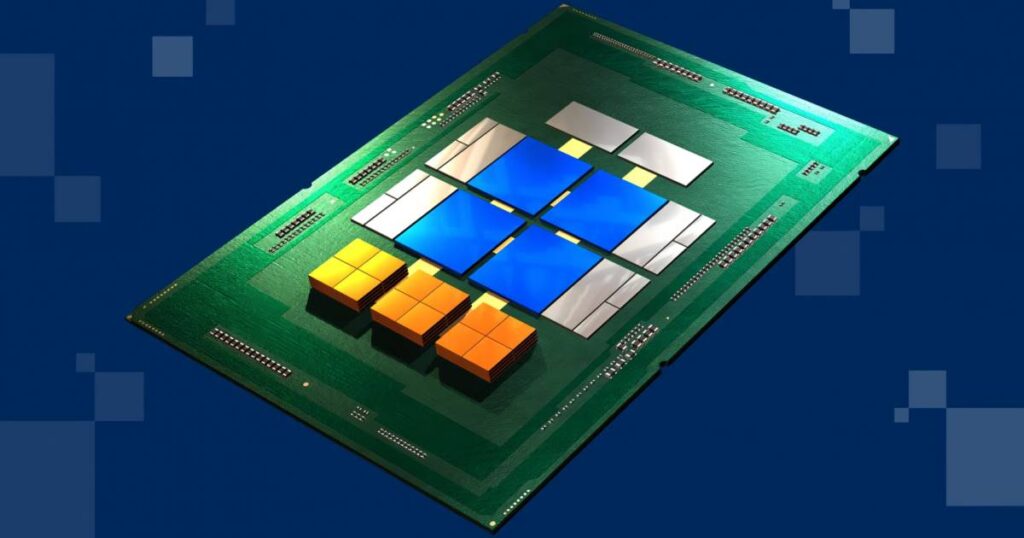

El concepto del Universal Chiplet Interconnect Express o UCIe es simple, se trata de crear un interposer estándar, el cual permita combinar varios chiplets de distintas marcas encima del mismo. Tened en cuenta que el Interposer es la pieza no solo donde se montan los diferentes chiplets, sino que se encargan también de la intercomunicación entre los diferentes componentes, lo que permite crear microprocesadores complejos a medida de cada cliente con piezas distintas, pero sobre todo, poder utilizar ciertos componentes entre diseños dispares.

En su versión del 1.0, el UCIe se basa en una versión 3DIC del protocolo PCI Express 5.0 con coherencia de memoria, es decir, en CXL. La ventaja en cuanto al consumo es más que clara, de 8 pJ/bit en una interfaz PCIe estándar a 0,43 pJ/bit a la hora de comunicar en un interposer, pero con una densidad de ancho de banda 32 veces superior por mm². En total, 32 canales con la capacidad de entregar hasta 630 GB/s en total de comunicación interna. Es decir, el Compute Express Link en forma de interfaz PCIe estándar no tiene futuro, pero va a ver su utilidad en la creación de sistemas basados en chiplets.

Ahora bien, los sistemas heterogéneos que combinen productos de varias marcas distintas en una sola pieza serán una rareza. Pensad en productos como consolas de videojuegos de próxima generación, donde ciertos elementos a medida y exclusivos de cada sistema irán en chiplets aparte.

Los futuros chiplets de AMD tendrán componentes de terceros

La empresa de Lisa Su, de la mano de su Director Técnico, Mark Papermaster, ha hablado de sus planes de usar el estándar UCIe en futuros diseños de la marca basados en chiplets. En concreto, lo hizo hace unos días en un vídeo publicado en el canal de YouTube oficial de AMD, y, sinceramente, nos sorprende que haya pasado desapercibido.

Las palabras de Papermaster, respecto al UCIe fueron las siguientes:

Los aceleradores de dominio específico, esa es la mejor manera de tener rendimiento por vatio. Así que son algo esencial para progresar. No puedes permitirte hacer un producto específico para cada uno de estos dominios, por lo que ello que lo que podemos hacer es tener un ecosistema de chiplets, una biblioteca esencialmente.

A lo que se refiere el CTO de AMD, es que ellos no pueden crear un chip distinto para cada solución. Por lo que el futuro se basará en diseños donde varios productos compartirán una serie de piezas en común y unas pocas a medida. Estás últimas seguramente diseñadas internamente por el fabricante del producto, y más ahora con la emergencia de RISC-V. Por lo que no os extrañe ver consolas next gen compuestas por chiplets.