Cambios significativos en la muestra de ingeniería de Arrow Lake-S

La primera muestra de ingeniería de Arrow Lake-S ya se encontrarían circulando y siendo puestas a prueba, lo que indica que la rampa de lanzamiento de la próxima CPU para el socket LGA 1851, y, por tanto, para ordenadores de escritorio. ¿Qué nuevos datos nos ha dado la versión ES de los futuros Core Ultra de segunda generación?

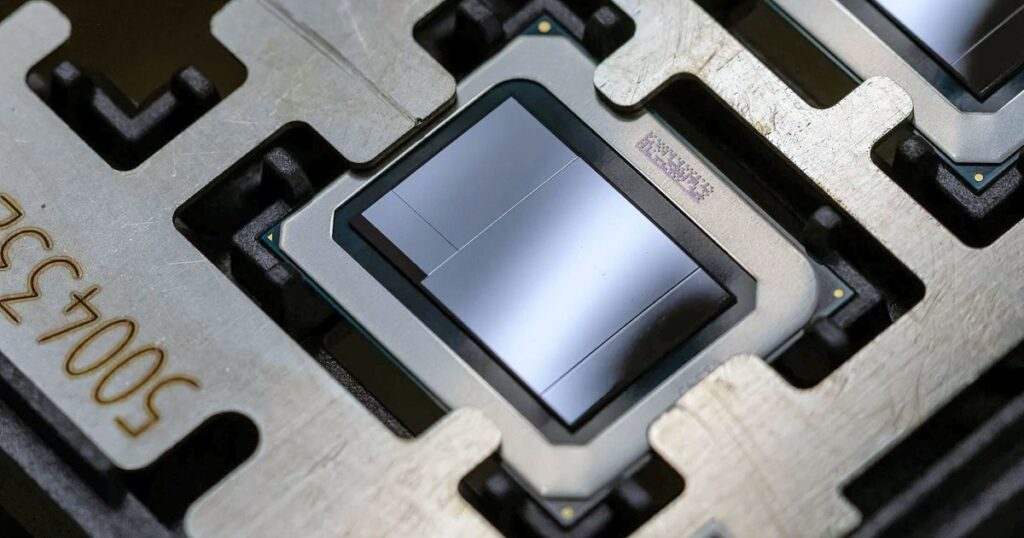

Se filtra una muestra de ingeniería del Arrow Lake-S

El usuario de Twitter InsLabx64 ha descubierto en las bases de datos de Intel información sobre las muestras de ingeniería de Arrow Lake-S, la versión para escritorio de la futura CPU de Intel, aunque se desconoce por el momento que modelo completo, hay una serie de datos que se han podido saber.

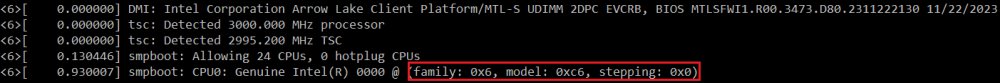

El primer punto es el número de hilos, en la información del benchmark interno lo cuenta como 24 CPU, pero no significa que tengamos 24 chips, sino que dentro de la misma se procesan 24 hilos. Recordad que cada hilo de ejecución se ve como un núcleo de la CPU, por este tipo de aplicaciones. Pues bien, dicha cifra vendría a confirmar la eliminación del HyperThreading, que es como Intel llama a la capacidad multihilo, de los P-Cores. Algo que hasta el momento era un rumor.

La otra ausencia en la muestra de ingeniería de Alder Lake-S la eliminación de las instrucciones AVX-512, pero se desconoce si es por el hecho de que la CPU carece de las unidades de ejecución y registros necesarios para ello o por una desactivación por el firmware del propio chip. En todo caso, tanto el multihilo como las instrucciones SIMD de 512 bits son dos de las cosas que más disparan el consumo energético en un microprocesador.

En cuanto a velocidades de reloj, hemos de partir que las muestras de ingeniería no suelen funcionar a las frecuencias finales, por lo que si bien está funciona a 3 GHz, no se trata de un reflejo final de lo que veremos en la versión final de la CPU.